昂洋科技

电子元器件一站式采购平台

昂洋科技

电子元器件一站式采购平台

昂洋科技

电子元器件一站式采购平台

昂洋科技

电子元器件一站式采购平台

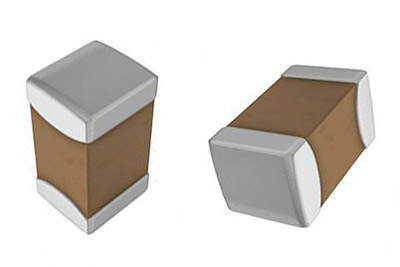

顺络CC1206KKX7RBBB104是一款采用X7R介质的1206贴片陶瓷电容,其额定电压为10V,容量为0.1μF(104),适用于高频电路中的去耦或滤波场景。然而,X7R介质电容在高频应用中可能因介质损耗和等效串联电阻(ESR)导致信号衰减或发热。以下从材料特性、电路设计及工艺优化三方面提出降低高频损耗的解决方案。

一、材料特性与选型优化

X7R介质电容的容量温度系数为±15%(-55℃~+125℃),但其介质损耗因数(DF)通常在0.02左右,高频下ESR会显著增加。为降低损耗,可采取以下措施:

替换为低损耗介质:若电路对损耗敏感,可考虑选用NPO(COG)介质电容(如顺络NPO系列),其DF可低至0.001以下,且容量温度系数极低(±30ppm/℃),适合高频振荡或耦合场景。

选择高电压型号:CC1206KKX7RBBB104额定电压为10V,若电路工作电压较低(如3.3V),可选用更高电压等级的同规格电容(如25V),以降低电场强度对介质损耗的影响。

二、电路设计与布局优化

高频损耗的降低需结合电路拓扑与PCB布局:

并联低ESR电容:在CC1206KKX7RBBB104旁并联一颗小容量NPO电容(如10pF~100pF),利用NPO电容的低ESR特性覆盖高频段,而X7R电容负责中低频滤波,形成宽频带低阻抗路径。

缩短高频回路路径:电容的安装位置应尽量靠近芯片电源引脚,减少引线电感。例如,在数字电路中,0.1μF电容与10nF NPO电容并联时,需确保两者引脚长度均小于3mm,以降低寄生电感对高频阻抗的影响。

避免热耦合:高频电容易因发热导致损耗增加,需远离大功率元件(如功率MOS管、电感),并保持至少5mm间距。

三、工艺与测试验证

优化焊接工艺:回流焊温度曲线需严格控制在245℃±5℃(峰值),避免高温导致电容内部电极损伤,进而增加ESR。焊接后需进行X-Ray检测,确保无空焊或短路。

高频阻抗测试:使用网络分析仪测试电容在100MHz~1GHz频段的阻抗特性,验证其是否满足设计要求。例如,CC1206KKX7RBBB104在100MHz时的阻抗应低于1Ω,若实测值偏高,需检查PCB布局或更换电容型号。

热设计验证:通过红外热成像仪监测电容表面温度,确保其在最大工作电流下温升不超过15℃。若温升过高,可增加散热焊盘或改用更高耐温等级的电容(如X7R 150℃型号)。

四、替代方案与成本平衡

若CC1206KKX7RBBB104仍无法满足高频损耗要求,可考虑以下替代方案:

MLCC与钽电容混合使用:在电源滤波中,用钽电容(如AVX TPS系列)负责低频大容量储能,MLCC负责高频去耦,但需注意钽电容的耐压降额(通常为额定电压的50%)。

薄膜电容替代:对于超高频场景(如GHz级),可选用聚丙烯薄膜电容(如EPCOS B32674系列),其DF可低至0.0001.但成本较高。

通过材料选型、电路优化及工艺控制,可显著降低顺络CC1206KKX7RBBB104在高频应用中的损耗,提升电路性能与可靠性。

上一篇: 合金电阻大电极与小电极的区别解析

下一篇: 高频电路中使用电解电容的注意事项